- Procedural Assignment

Quick links

System verilog, data type, typedef methods, loop statement.

In our previous blog, we talked about the procedural assignment in Verilog. These are almost the same in System Verilog, so let’s discuss that in this blog.

Procedural assignments come in the form of procedural blocks like “always”, “initial,” “task,” and “function.”

To regulate when assignments are assessed and/or assigned, event controls, delay controls, if…else statements, case statements, looping statements, and so on can all be utilized.

Any expression that evaluates a value can be used as the RHS of the procedural assignment. However, keep in mind that the assignment’s LHS may limit what is a permitted expression on the RHS.

The LHS can be a solitary variable, an aggregate variable, a bit-select, a part-select, a packed array slice, or an unpacked array slice.

Procedural assignments are classified into the following categories:

Blocking assignment

Non-blocking assignment.

The operator ” =” is the most basic form of assignment. But in this blog, we will introduce you to other operators such as +=, =, e.t.c.

Throughout this blog, we’ve seen blocking assignments. As a result, we shall desist from further debate. Non-blocking is a new concept, and we must distinguish between the two. So we will shortly discuss the blocking assignment.

Blocking assignment statements are executed in sequential order. The execution of the following statement is halted until the current assignment operation is completed.

So let’s understand blocking assignments with an example.

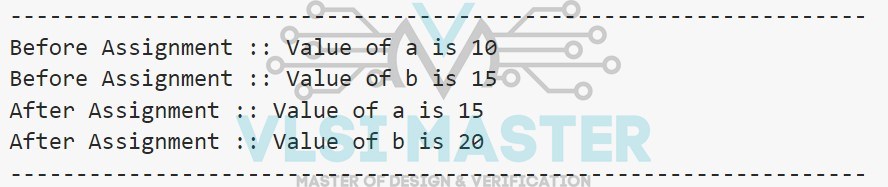

Figure 1 shows the output of the above code of blocking assignment.

Fig 1 Blocking assignment output

The non-blocking assignment permits assignment schedule without interfering with the flow of the procedure.

The non-blocking procedural assignment statement can be used when many variable assignments can be made within the same time step without regard for order or dependency on each other.

Non-blocking syntax is:

variable_name <= [delay_or_event_control] expression.

The non-blocking assignment operator is <=. The non-blocking assignment operator is the same as the relational operator less-than-or-equal-to.

However, non-blocking is determined by the context in which it appears.

Non-blocking execution may be divided into two steps: 1. At the start of the time step, evaluate the RHS of the non-blocking statement. 2. After the time step, evaluate the LHS of the non-blocking statement.

Consider the following example. We’ll compare blocking to non-blocking:

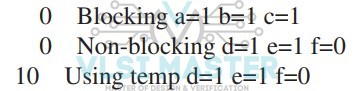

The above code will compare blocking and non-blocking assignments and their output is shown in figure 2.

Fig 2: Blocking and Non-blocking example output

Let me explain this code for more explanation.

There are three “initial” blocks. The first is a blocking assignment: a = b; c = a; With this assignment, “b” is allocated to “a,” and the new value of “a” is assigned to “c.” As a result, the new value of “a” (from a = b) is given to “c” (c = a). Because a = 0 and b = 1, a = b results in a = 1, and c = a results in c = 1.

As a result, the following appears in the simulation log:

0 Blocking a=1 b=1 c=1

The non-blocking assignment, on the other hand, operates as follows: Consider two flops linked in series: d <= e; f <= d; Because they are non-blocking, the two assignments run concurrently. The first assignment does not prevent the second task from being completed. The current value of “e” is assigned to “d,” and the current value (before the assignment d = e) of “d” is assigned to “f.”

With d = 0 and e = 1, the simulation log shows the following:

0 Non-blocking d=1 e=1 f=0

Consider the preceding non-blocking as the extended version: e = temp; f = d; d = temp;

When d = 0 and e = 1, the current value of “e” (= 1) is stored in the temp variable (temp = 1). The current “d” (= 0) value is then allocated to “f” (f = d). As a result, f = 0, and the value of “e” saved in “temp” is assigned to “d.” So, d = 1.

As a result, the simulation log displays the following:

10 Using temp d=1 e=1 f=0

It should be noted that this is the same outcome as a non-blocking assignment:

So, using a simple and effective example, we can quickly grasp the concept of blocking and non-blocking assignments.

As a result, we summarise the entire blog with a few questions.

- What exactly do you mean when you say “procedural assignment”?

- How many different kinds of procedural assignments are there?

- What exactly is a blocking assignment?

- How does a non-blocking assignment differ from a blocking statement?

Please Login or Register to comment on this post

Only fill in if you are not human

Recent Blogs

- Privacy Policy

- @VLSI_Master

- VLSI-Master

Copyright © 2021 All rights reserved

A procedural assignment updates the value of register data types.

Description:

Procedural assignments are used for updating register data types and memory data types.

The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered. In a begin-end sequential statement group, execution of the next statement is blocked until the assignment is complete.

In a non-blocking procedural assignment, the expression is evaluated when the statement is encountered, and assignment is postponed until the end of the time-step. In a begin-end sequential statement group, execution of the next statement is not blocked and may be evaluated before the assignment is complete. A group of statements with a non-blocking assignment has similar functionality as a group of statements within a fork-join block.

The left-hand side of a procedural assignment should be one of the following:

- Register data type: reg , integer , time , real or realtime .

- Bit-select of reg , integer or time .

- Part-select of reg , integer or time .

- Memory word.

- Concatenation of any of the above.

When the right-hand side evaluates to a fewer bits than the left-hand side, the assignment to a reg does not sign-extend.

The evaluation of the assignment is delayed by the delay when the delay is specified before the register name. When the delay is specified before the expression, the expression is evaluated when the statement is encountered, and assigned in the time-step specified by the delay.

Continuous assignment , Expression , Net data type

Verilog: Continuous & Procedural Assignments

Continuous Assignment

Continuous assignment is used to drive a value on to a net in dataflow modeling. The net can be a vector or scalar, indexed part select, constant bit or part select of a vector. Concatenation is also supported with scalar vector types.

module Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] dout; input valid1,valid2,wr;

wire valid; wire [31:0] addr;

//Net (scalar) continuous assignment assign valid = valid1 | valid2;

//Vector continuous assignment assign addr[31:0] = addr1[31:0] ^ addr2[31:0];

//Part select & Concatenation in Continuous assignment assign dout[31:0] = (valid & wr) ? {din[31:2],2'b11} : 32'd0;

Regular & Implicit Assignment

Regular continuous assignment means, the declaration of a net and its continuous assignments are done in two different statements. But in implicit assignment, continuous assignment can be done on a net when it is declared itself. In the below example, `valid` is declared as wire during the assignment. If signal name is used to the left of the continuous assignment, an implicit net declaration will be inferred. In the below code `dout` is not declared as net, but it is inferred during assignment.

module Implicit_Conti_Assignment (addr1,addr2,wr,din,valid1,valid2,dout); input [31:0] addr1,addr2; input [31:0] din; output [31:0] dout; input valid1,valid2,wr;

//Net (scalar) Implict continuous assignment wire valid = (valid1 | valid2);

//Implicit net declaration -dout assign dout[31:0] = (valid & wr) ? {din[31:2],2'b11} : 32'd0;

Related Questions

コミュニティ フィードバック

IMAGES

VIDEO

COMMENTS

Note: IEEE is considering depreciating procedural continuous assignment, so in the future it will likely become illegal syntax. IEEE Std 1800-2012 C.4.2 Procedural assign and deassign statements : The procedural assign and deassign statements can be a source of design errors and can be an impediment to tool implementation.

The LHS of an assignment in a procedural block must be of type reg.Procedural assignment statements assign values to reg, integer, real, or time variables and can not assign values to wire.Note that reg can hold or store some value depending on some triggering event, while wire cannot store any value.. Here, k is holding some value till the addr signal changes.

Tour Start here for a quick overview of the site Help Center Detailed answers to any questions you might have Meta Discuss the workings and policies of this site

In Verilog: Nets are driven by any number of continuous assigns or ports - conflict resolution determines the final value if multiple drivers exists. Variables are driven by procedural assignments. In SystemVerilog: Nets are driven by any number of continuous assigns or ports - conflict resolution determines the final value if multiple drivers ...

(VERI-1100) procedural assignment to a non-register 'nextstate' is not permitted. The problem is mostly with the case statement. I am genuinely confused. My design clearly cannot be implemented using clocked registers for these signals. I've tried several versions, with assign, with and without always and can't get it to compile.

The non-blocking procedural assignment statement can be used when many variable assignments can be made within the same time step without regard for order or dependency on each other. Non-blocking syntax is: variable_name <= [delay_or_event_control] expression. The non-blocking assignment operator is <=.

In this series, we will use Verilog, as it is supported by the yosys synthesis tool. Previously, we used continuous assignment statements to construct basic digital logic circuits, including a full 1-bit adder. In this tutorial, we present one possible solution to creating a clock divider in an FPGA using procedural assignment statements. Video.

ERROR: [Synth 8-2577] procedural assignment to a non-register some_signal is not permitted, left-hand side should be reg / integer / time / genvar; Why do I need to define some_signal as a reg type? Thank you in advance for your responses and time! -anm

Looks like you have you direction reversed for the rx_data and tx_data parallel ports of the SPI module. Generally speaking, parallel rx_data should be the output of the SPI interface module, i.e. received data from the serial wires of the interface gets parallelized in the module, and then output to the rest of the FPGA.

Description: Procedural assignments are used for updating register data types and memory data types. The expression in a blocking procedural assignment is evaluated and assigned when the statement is encountered. In a begin-end sequential statement group, execution of the next statement is blocked until the assignment is complete. In a non ...

Procedural assignments can come in two forms: blocking (=) and non-blocking (<=). A blocking assignment (=) will not allow the execution to proceed until the assignment has been completed. On the other hand, a non-blocking assignment (<=) schedules the assignment to occur at the end of the current time step and allows the execution to continue ...

There are two types of procedural assignments called blocking and non-blocking. Blocking assignment, as the name says, gets executed in the order statements are specified. The "=" is the symbol used for blocking assignment representation. Non-blocking assignment allows scheduling of assignments. It will not block the execution.

CAUSE: In a procedural assignment at the specified location in a Verilog Design File (), you assigned a value to the specified object, which was declared with a net data type (wire, wand, and so on) rather than with a variable data type (reg, integer, and so on).In Verilog HDL, you must use continuous assignments when targeting nets, and procedural assignments when targeting variables.

This is why regardless of what happens in the block the Verilog spec simply mandates that any variable used in a procedural block must be able to store a value. In response to your comment, there are non-procedural ways of doing things which do not require registers - any combinational circuit can be defined without the need for procedural blocks.

Variables are driven by procedural assignments. In SystemVerilog: Nets are driven by any number of continuous assigns or ports - conflict resolution determines the final value if multiple drivers exists. Variables are driven by procedural assignments or a single continuous assign or port (not both) - since there is only one continuous assign ...

In general be cautious about mixing blocking and non-blocking assignments, what you have is fine, but it can be a bit more confusing to read which can lead to bugs being introduced if someone modifies it later. I would recommend adding comments saying something like: "temp signal for internal (to this block use only) using blocking assignments".

Yes, they are equivalent. IEEE Std 1364-2005, section 6.2 Procedural assignments states:...procedural assignments put values in variables. The assignment does not have duration; instead, the variable holds the value of the assignment until the next procedural assignment to that variable. You do not need to use the 2nd code example.

I am working on a cordic project, but it seems that I am having trouble with the 16 to 1 multiplexer. I already tried re-writing the code, but still no clue. module mux_16(operand, reg_in, select...

tempreg is storing values and will not be purely combinational logic. Use the template below, and use non-blocking assignments to tempreg. If you don't use the clock, then you will have complex latching logic. If you don't use non-blocking, then there is a potential race condition in the Verilog simulator.

However a wire cannot be assigned in a procedural code (ex always block). So you need to think how to assign some bits to from a module and other from procedural. \$\endgroup\$ - Greg

Verilog:Procedural Continuous Assignment to register is not supported. 2 SystemVerilog assigning values to generated blocks. ... Procedural Continuous Assignment to register is not supported. 2 SystemVerilog assigning values to generated blocks. 1 Output port continuous assignment problem. 2